新入荷

再入荷

【ふるさと割】 VLSI Placement and Global Routing Using Simulated Annealing 数学

タイムセール

タイムセール

終了まで

00

00

00

999円以上お買上げで送料無料(※)

999円以上お買上げで代引き手数料無料

999円以上お買上げで代引き手数料無料

通販と店舗では販売価格や税表示が異なる場合がございます。また店頭ではすでに品切れの場合もございます。予めご了承ください。

商品詳細情報

| 管理番号 |

新品 :68079158792

中古 :68079158792-1 |

メーカー | 60b7fed4 | 発売日 | 2025-05-10 09:59 | 定価 | 6800円 | ||

|---|---|---|---|---|---|---|---|---|---|

| カテゴリ | |||||||||

【ふるさと割】 VLSI Placement and Global Routing Using Simulated Annealing 数学

VLSI Placement and Global Routing Using Simulated Annealing,

VLSI Placement and Global Routing Using Simulated Annealing, A 300 nW 10 kHz Relaxation Oscillator with 105 ppm,

A 300 nW 10 kHz Relaxation Oscillator with 105 ppm, A 300 nW 10 kHz Relaxation Oscillator with 105 ppm,

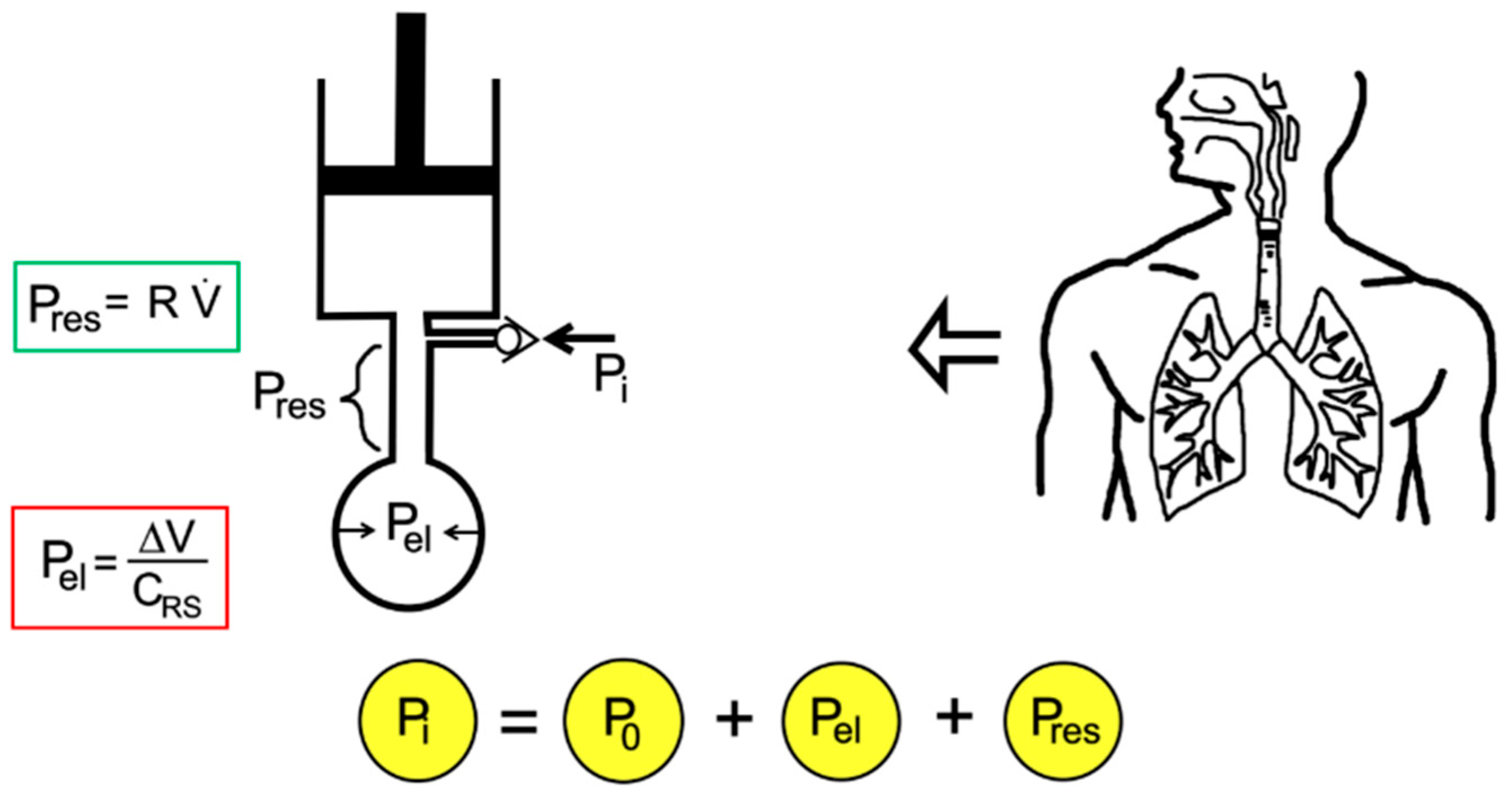

A 300 nW 10 kHz Relaxation Oscillator with 105 ppm, Validation of a Simulink Model for Simulating the Two,

Validation of a Simulink Model for Simulating the Two, Logic Analyser on Multisim to demostrate 4 Bit Counter

Logic Analyser on Multisim to demostrate 4 Bit Counter0015254 算法便覧 巻1,3、4、6 浪華武田先生著 武田真元

リケンあめ色玉ねぎドレッシング 3本✫マコーミックフレンチドレッシング2本セット

![[A11823723]部分矯正: その臨床応用のすべて](https://auctions.c.yimg.jp/images.auctions.yahoo.co.jp/image/dr000/auc0512/user/edc343cdefc90ed400aee3f558c4826ff1d13873ed0e7cf61e9f955abed75d52/i-img842x1200-17343320859908hxsxrw110616.jpg)

![[A12291842]愛光高等学校 入学試験問題集 2024年春受験用 (プリント形式のリアル過去問で本番の臨場感!) (愛媛県私立高等学校入学試験問](https://auctions.c.yimg.jp/images.auctions.yahoo.co.jp/image/dr000/auc0504/users/d4fab30473777a8019148ae00533fa27693af6d4/i-img353x500-1714051395c5s03w214854.jpg)